JEDEC announced it has finalized the DDR4 memory standard. The first DDR4 memory modules for servers are anticipated next year, but widespread adoption among consumers isn't anticipated until 2015.JEDEC Solid State Technology Association, the global leader in the development of standards for the microelectronics industry, today announced the initial publication of its widely-anticipated Synchronous DDR4 (Double Data Rate 4) standard.

JEDEC DDR4 (JESD79-4) has been defined to provide higher performance, with improved reliability and reduced power, thereby representing a significant achievement relative to previous DRAM memory technologies. The new DDR4 standard is available for free download from the JEDEC website at http://www.jedec.org/standards-documents/results/jesd79-4%20ddr4.

DDR4 offers a range of innovative features designed to enable high speed operation and broad applicability in a variety of applications including servers, laptops, desktop PCs and consumer products. In addition to the advantages described later in this release, the new technology has been defined with a goal of simplifying migration and enabling adoption of an industry-wide standard.

To facilitate comprehension and early adoption of the DDR4 standard, JEDEC is hosting a two-day DDR4 Technical Workshop in Santa Clara, CA on October 30 and 31. For online registration and agenda information visit: http://www.jedec.org/ddr4workshop.

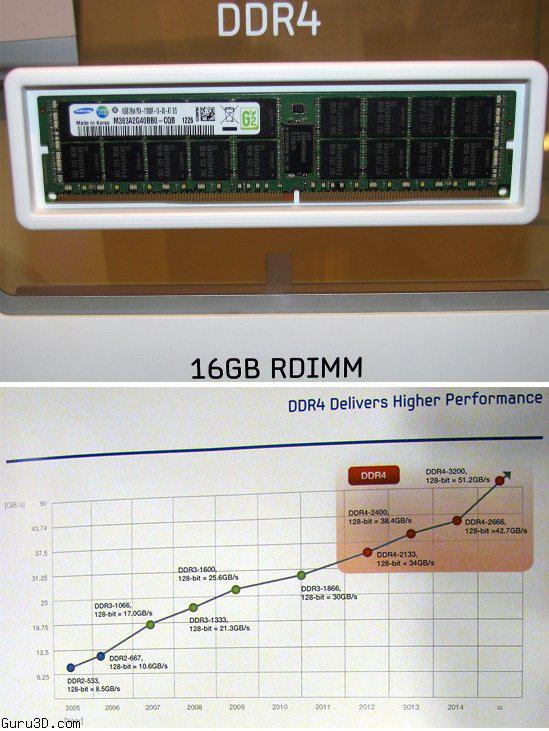

The per-pin data rate for DDR4 is specified as 1.6 giga transfers per second to an initial maximum objective of 3.2 giga transfers per second. With DDR3 exceeding its original targeted performance of 1.6 GT/s, it is likely that higher performance speed grades will be added in a future DDR4 update. Other DDR4 attributes tightly intertwined with the planned speed grades, enabling device functionality as well as application adoption, include: a pseudo open drain interface on the DQ bus, a geardown mode for 2,667 MT/s per DQ and beyond, bank group architecture, internally generated VrefDQ and improved training modes.

The DDR4 architecture is an 8n prefetch with two or four selectable bank groups. This design will permit the DDR4 memory devices to have separate activation, read, write or refresh operations underway in each unique bank group. This concept will also improve overall memory efficiency and bandwidth, especially when small memory granularities are used. More information about additional features may be found on the JEDEC website.

In addition, DDR4 has been designed in such a way that stacked memory devices may prove to be a key factor during the lifetime of the technology, with stacks of up to 8 memory devices presenting only a single signal load.

Joe Macri, Chairman of JEDEC’s JC-42.3 Subcommittee for DRAM Memories, said: “The publication of the JEDEC DDR4 standard represents the culmination of years of dedicated effort by memory device, system, component and module producers worldwide. The new standard will enable next generation systems to achieve greater performance, significantly increased packaging density and improved reliability - with lower power consumption.”

“The industry has been looking forward to the publication of this standard for some time,” noted Desi Rhoden, Chairman JC-42 Memory Committee and Executive VP Montage Technology. “The current publication will provide early adopters with the critical information required to utilize the emerging DDR4 devices. Subsequent publications are planned to address material not yet finalized in time for this publication. As with all JEDEC standardization activities, industry participation is highly valued – companies interested in participating in JEDEC may visit the JEDEC website at www.jedec.org or call 703-907-7560 for more information.”

Industry Support for DDR4

“Following finalization of JEDEC DDR4 specifications, Samsung continues to provide highly advanced-performance, low-power DRAM solutions in furthering the development of state-of-the-art next-generation green IT systems,” said Byungse So, Senior Vice President, Memory Product Planning and Application Engineering, Device Solutions, Samsung Electronics. “Together with our global customers, we will continue to develop economic IT systems with high energy-efficiency to enlarge the premium memory market in support of the most advanced computing modules and solutions.”

"The publication of the DDR4 standard is a great milestone leading up to the launch of this next generation of DRAM," said Robert Feurle, vice president for Micron's DRAM marketing. "Improvements in performance and power consumption make DDR4 an attractive memory solution for the next generation of enterprise and consumer products, and we look forward to driving this technology into the marketplace."