Multi-die chips are what we're talking about to be able to fight off Moore's Law in the future. AMD already is using the technology to connect multiple processors in Threadripper and for servers, Epyc, but also Intel with Kaby Lake-G. However new in research are Chiplets, are parts of chips stacked together on an interposer that form the entire chip.

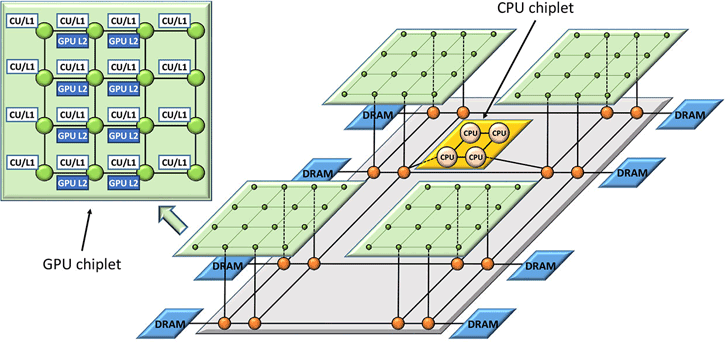

One of the bigger issues at hand when manufacturing large CPU/GPU dies is that yields decrease and costs goes up. As you create larger products, that is an issue. So why not combine multiple dies onto one merged package? In an example, as posted in a paper (below) you can see four GPUs with a CPU partition combined into one chip. The data is then moved via an interposer, basically sending the right data to the right place. AMD published a new study in which it studied chiplets for new multi-die CPU and GPU designs as posted at spectrum.ieee.org, check it out:

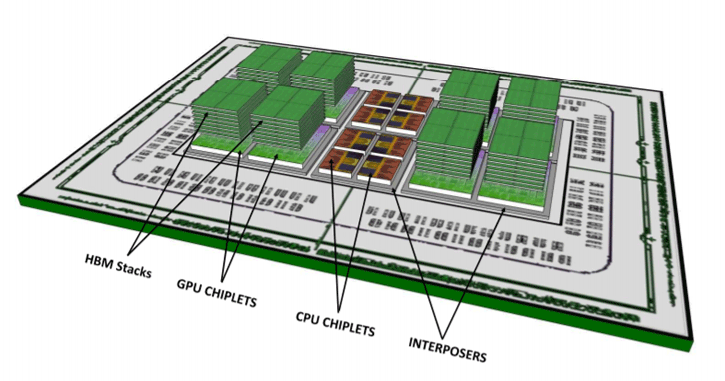

The time may be coming when computers and other systems are made not from individually packaged chips attached to a printed circuit board but from bare ICs interconnected on a larger slice of silicon. Researchers have been developing this concept called “chiplets” with the idea that it will let data move faster and freer to make smaller, cheaper, and more tightly integrated computer systems. The idea is that individual CPUs, memory, and other key systems can all be mounted onto a relatively large slice of silicon, called an active interposer, which is thick with interconnects and routing circuits.

could be designed so that they never have deadlocks,” says Loh. “But once I put them together, there are now new paths and new routes that no individual had planned for ahead of time.” Trying to avoid these new deadlocks by designing all the chiplets together with a particular interposer network in mind would defeat the advantages of the technique: Chiplets, then, couldn’t be designed and optimized easily by separate teams, and they couldn’t easily be mixed and matched to quickly form new systems. At the International Symposium on Computer Architecture earlier this month, engineers at AMD presented a potential solution to this impending problem.

The AMD team found that deadlocks on active interposers basically disappear if you follow a few simple rules when designing on-chip networks. These rules govern where data is allowed to enter and leave the chip and also restricts which directions it can go when it first enters the chip. Amazingly, if you follow those rules you can pretend everything else on the interposer—all the other logic chiplets, memory, the interposer’s own network, everything—is just one node on the network. Knowing that, separate teams of engineers can design chiplets without having to worry about how the networks on other chiplets work or even how the network on the active interposer works.

It may be some time before this trick is even needed. So-called passive interposers—silicon that contains interconnects but no network circuits—are already in use; AMD has been using one for its Radeon R9 series, for example. But adding an intelligent network to the interposer could lead to a big change in how systems are designed and what they can do.

AMD is looking into chiplets to connect future CPUs and GPUs