Page 3

A truly dope Ring

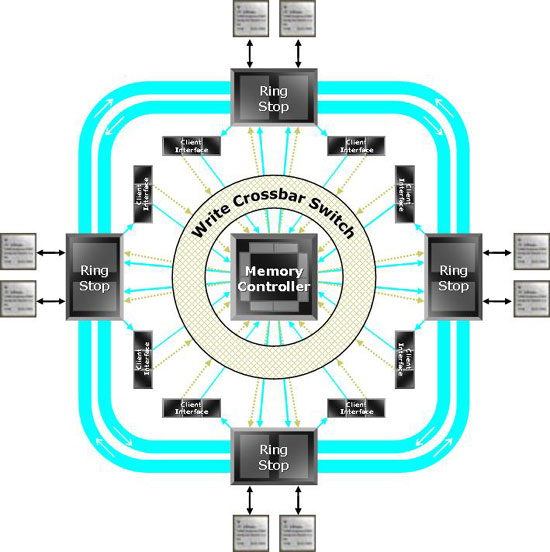

Beside the big internal architectural overhaul throughout the chip design, one of the biggest and most impressive changes in the X1x00 series simply has to be the new memory controller. It seriously is a piece of art if you study closer. Once we got the specs presented to us I immediately had to think about the Creative Labs X-Fi, which we recently reviewed. Both products are of course completey different and have, well not very much in common except one thing, an internal ring bus design. Included onto the X1x00 series is a new memory controller that works on a very advanced manner.

I'll try to explain it in a very simple manner because the controller is so advanced you can easily get confused. Take for example a car, which in our case is a memory client request to the memory controller. Look at this entire procedure as a traffic, normally you have to deal with congestion at a certain point where it's busy at that crossing right ? If enough cars keep coming in you'll get congestion. What do you do with such traffic congestion/traffic jam? Yes indeed, everywhere in the world we build multi-lane traffic circles and insert traffic lights at the beginning crossings to prioritize and streamline traffic into the right direction.

Now think of the car (client data request) as traffic being sent to the ordinary crossing and in the new situation the traffic circle with traffic lights. Yes this is in laymen terms the way the new controller functions. Huge flows of data traffic are no longer launched towards the memory controllers where it's jammed up, it's now sorted based on priorty flag (at the proverbial traffic lights) and then send into the right direction over the traffic circle. If we color coded 4 data packets green, yellow , blue and orange then each color will have a certain priority, you tag the data request. If red is the color has the most priority it'll be prioritized and send to the most memory unit connected to the controller. If a 'ornage' data packet has less priority it would be managed in a slower stage. What the result of this in very laymen terms explained the new ringbus memory controller. It's way more dynamic in the manner it can handle its memory packets. The end result, a more efficient memory controller that will utilize available bandwidth to the maximum. And memory bandwidth is one of the biggest limitations in the graphics industry so a lot can be won here.

The new ringbus memory controller

The new ringbus memory controller

Another good thing to know is that the new memory controller can handle any kind of DDR memory, whether that is DDR1 or gDDR3 it will handle it fine. Next to that, and less important for you though, it should be very future proof as it's gDDR4 ready and probably can even work with gDDR5 which is in early design stages already. It has been built with that in mind. It can handle extremely high clocks, it's very dynamic and very efficient according to the theory. The design in all honesty looks like a classy piece of art. Of course the raw performance and effect on overall framerate will in the end have the final say.

| What is a shader ? |

| What do we need to render a three dimensional object; 2D on your monitor? We start off by building some sort of structure that has a surface, that surface is being built from triangles and why triangles? They are quick to calculate. How's each triangle being processed? Each triangle has to be transformed according to its relative position and orientation to the viewer. Each of the three vertices the triangle is made up of is transformed to its proper view space position. The next step is to light the triangle by taking the transformed vertices and applying a lighting calculation for every light defined in the scene. At last the triangle needs to be projected to the screen in order to rasterize it. During rasterization the triangle will be shaded and textured. |