Product innards / teardown

Product Innards

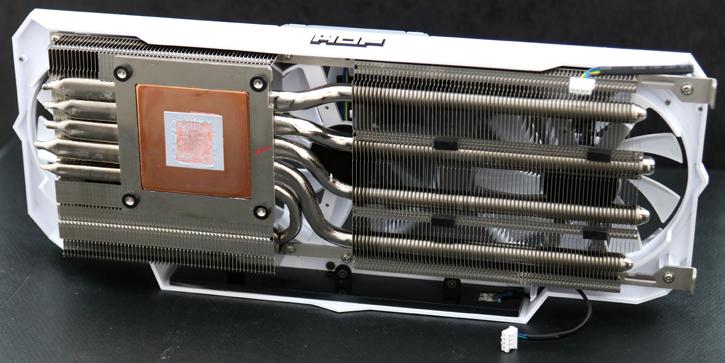

The cooling solution is impressive overall, it uses five heat-pipes that pass through a heatsink, with thermal paste tied to the all-copper block. That's as good as it gets really, and sure, that shows in the great cooling performance.

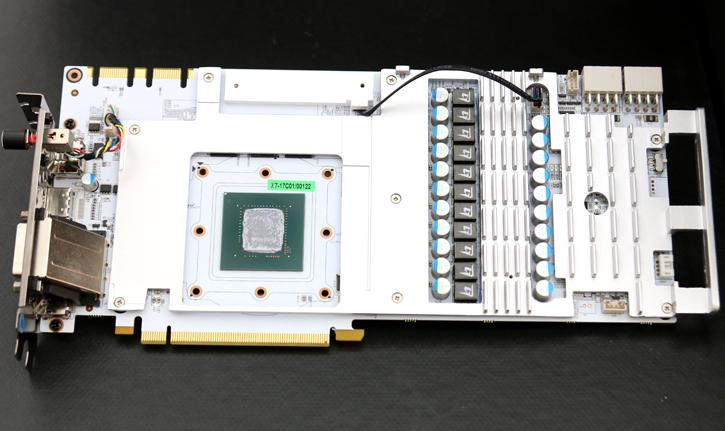

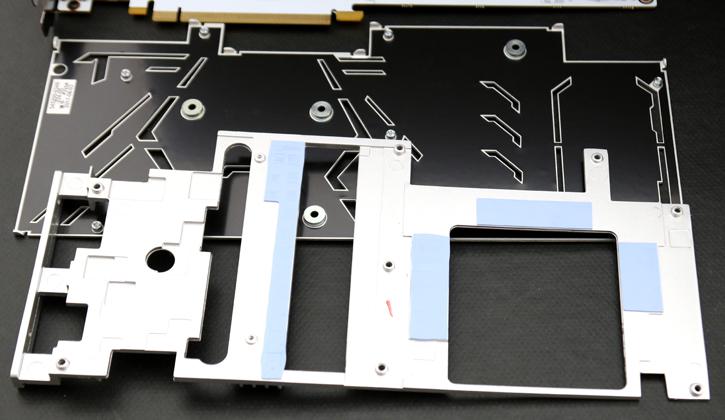

There is a cover plate on both the back and front side of the card if we look at the next photo:

Here we can see the GDDR5 memory is padded as well as some other points. Not all capacitors are in direct contact with the cooling block though that really doesn't show in thermals, as the card remains incredibly cool throughout all tests.

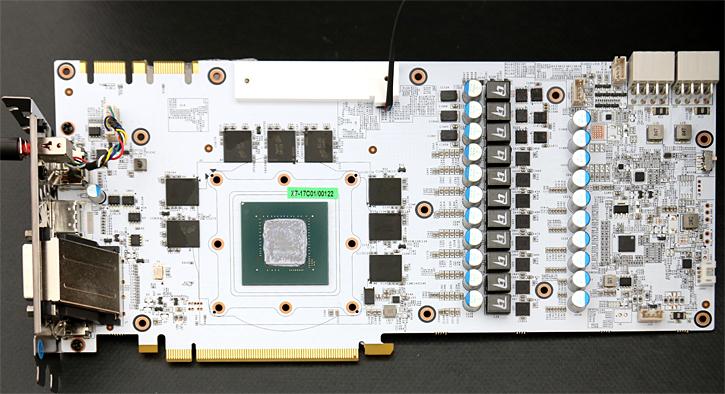

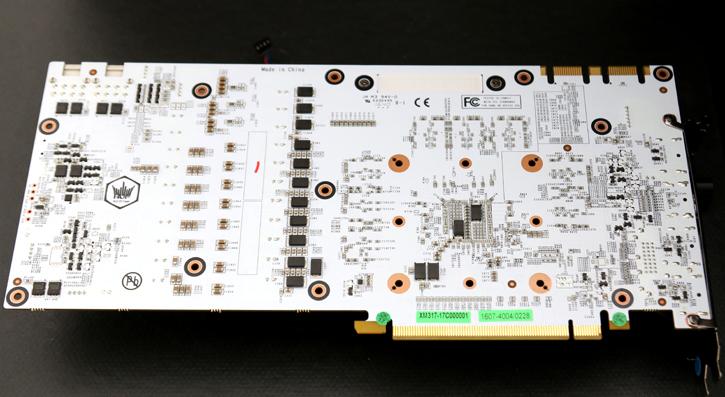

With the cooler blocks removed, we now have the full PCB visible. This is a very clean and white PCB design alright. Let's run through some of the components. Critical components are covered and padded, The power stages have padding as well and thus are cooled as well as most ICs. We can now see the power stages, GPU, memory and voltage phase-controller.

Also here a photo of the PCB backside, again this is a very clean layout.

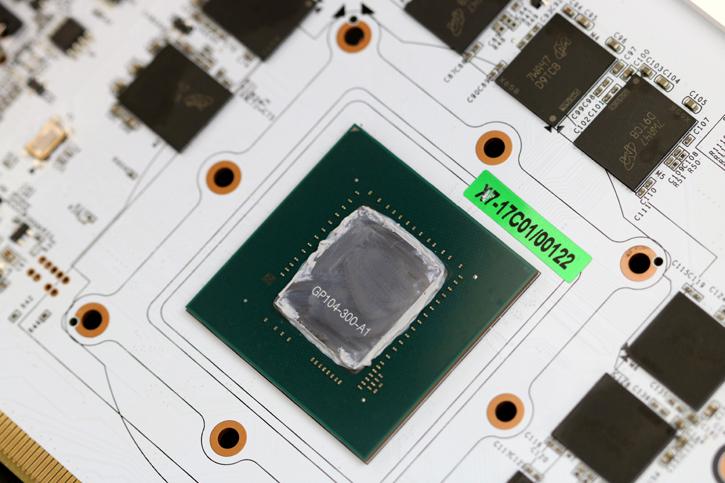

The GPU: here we have the GP104-300-A1 graphics processor from Nvidia with its 2,432 active CUDA / Shader Cores.

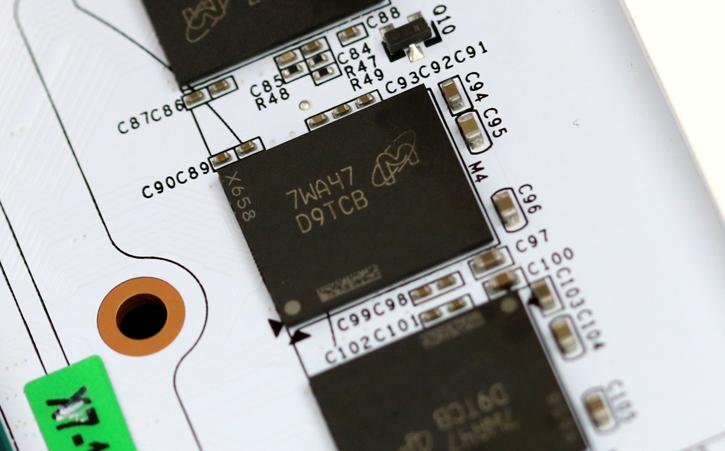

GDDR5 memory chips (D9TCB) are made by Micron and are specced to run at 8,008 MHz GDDR5 (effective data-rate). Tweaked you are looking at a capability of roughly 8,600 ~ 9,000 MHz (effective data-rate). It varies a little, the memory is not the most tweakable alright.

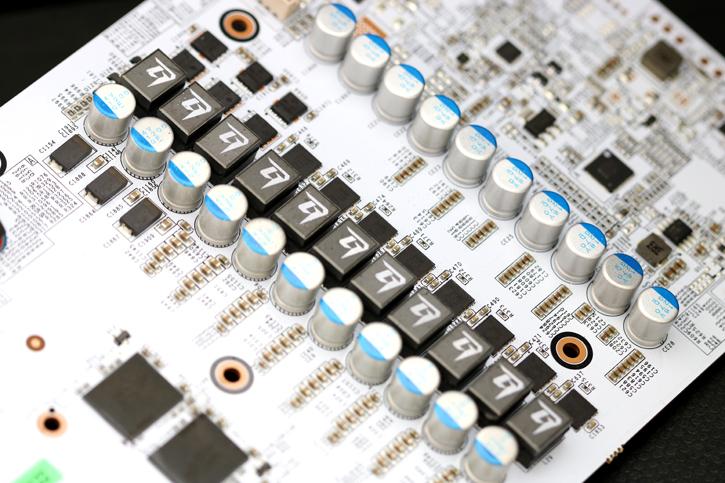

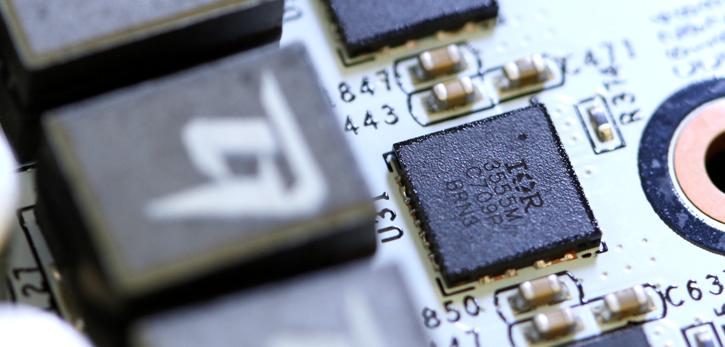

You can count them, eleven phases, eight for the GPU and three for memory. We first stumble into capacitors, in the middle where it reads that weird symbol, that is a molded inductor (chokes). These concrete alloy chokes help to decrease buzzing noises. And the square chips to the right are MOSFETs.

Let me show you:

For VRM, GALAX/KFA2 uses International Rectifier IR3555M 60A PowIRstage MOSFETs.

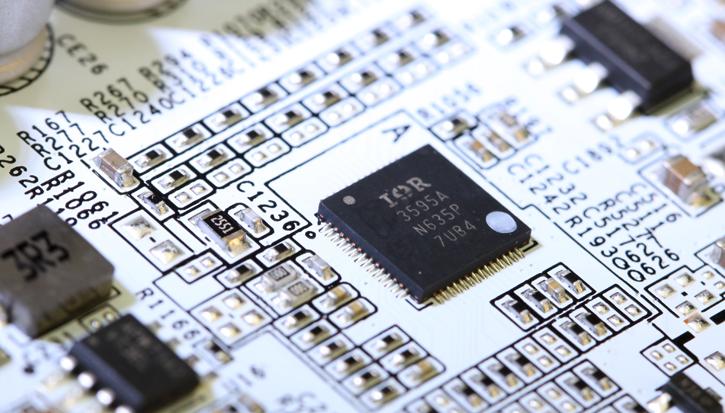

GALAX is using an International Rectifier IR3595A voltage controller, it offers eight-phases, single or 6+2 dual-loop configurable.

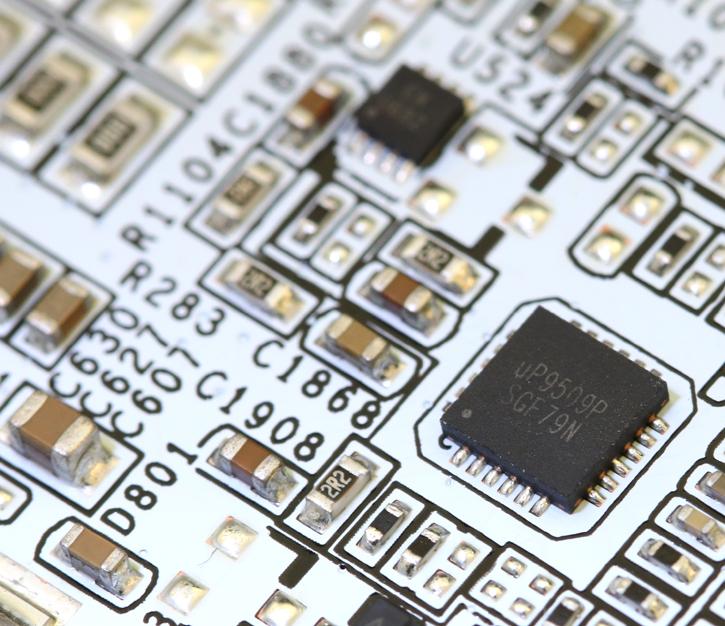

We still need phases for memory. There also is a UPI based uP9509 voltage regulator, this is regulating the three phases towards the memory.

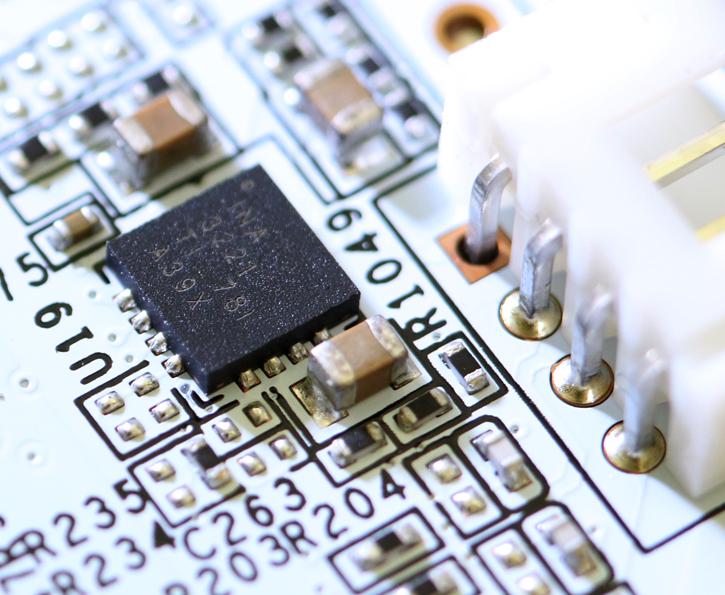

Current monitoring is enabled through a three-channel INA3221.