Memory timings - The 64-bit OS and your memory

What are memory timings?

Okay, allow me to explain a little what you will run into with memory timings. First off latency. We used the word numerous times already in this article. Latency is the time between when a request is made and the request is answered. I.E, if you are in a restaurant for a meal, the latency would be the time between when you ordered your meal to the time you received it. The faster your order is served, the better right? Therefore, in memory terms, it is the total time required before data (your meal) can be written to or read from the memory. Latency - lower is better.

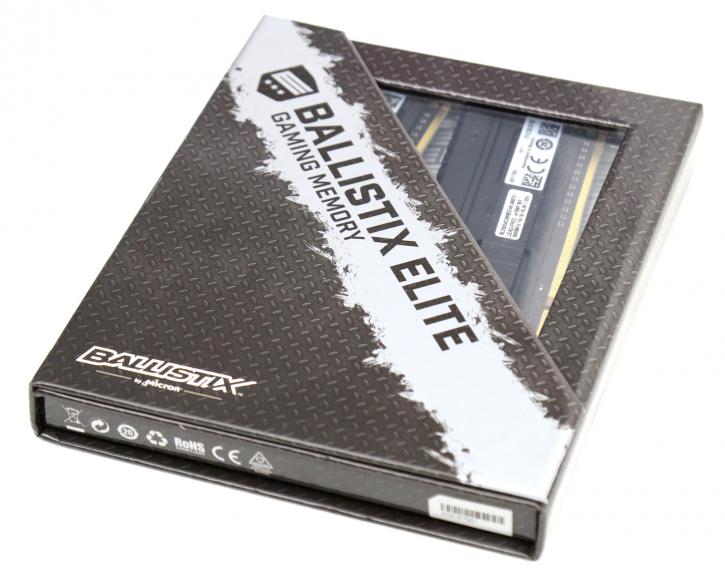

Say we notice on the packaging is this: CL16-18-18-38 1.35V (2T) for a memory kit. What do the numbers mean? Well, this refers to CAS-tRCD-tRP-tRAS CMD (respectively) and these values are measured in clock cycles.

CAS Latency

Undoubtedly, one of the most essential timings is that of the CAS Latency and is also the one most people can actually understand. Since data is often accessed sequentially (same row), the CPU only needs to select the next column in the row to get the next piece of data. In other words, CAS Latency is the delay between the CAS signal and the availability of valid data on the data pins (DQ). Therefore, the latency between column accesses (CAS), plays an important role in the performance of the memory. The lower the latency, the better the performance. However, the memory modules must be capable of supporting low latency settings.

tRCD

There is a delay from when a row is activated to when the cell (or column) is activated via the CAS signal and data can be written to or read from a memory cell. This delay is called tRCD. When memory is accessed sequentially, the row is already active and tRCD will not have much impact. However, if memory is not accessed in a linear fashion, the current active row must be deactivated and then a new row selected/activated. It is this example where low tRCD's can improve performance. However, like any other memory timing, putting this too low for the module can result in instability.

tRP

tRP is the time required to terminate one Row access and begin the next row access. Another way to look at this it that tRP is the delay required between deactivating the current row and selecting the next row. Therefore, in conjunction with tRCD, the time required (or clock cycles required) to switch banks (or rows) and select the next cell for either reading, writing or refreshing is a combination of tRP and tRCD.

tRAS

Memory architecture is like a spreadsheet with row upon row and column upon column with each row being 1 bank. In order for the CPU to access memory, it must first determine which Row or Bank in the memory that is to be accessed and activate that row via the RAS signal. Once activated, the row can be accessed over and over until the data is exhausted. This is why tRAS has little effect on overall system performance but could impact system stability if set incorrectly.

Command Rate

The Command Rate is the time needed between the chip select signal and the when commands can be issued to the RAM module IC. Typically, these are either 1 clock or 2. Memory testing is a process of trial and error, find and seek the maximum. This is pretty much a sucker for your free time.